Macrocell array - Wikipedia

Essentially, it is a small step up from the otherwise similar gate array, but rather than being a prefabricated array of simple logic gates, the macrocell array is a prefabricated array of higher …

techniques used to develop a macrocell array option. Built around macrocell flip-flops and gate structures, the counter features P inputs for programming, plus PE and CE inputs

ia601909.us.archive.org

Recent developments in Array . primitive gates for easier design and higher performance. circuit options. This note examines Motorola's Macrocell Ar¬ . ray concept with special emphasis on …

Macrocell array explained

Essentially, it is a small step up from the otherwise similar gate array, but rather than being a prefabricated array of simple logic gates, the macrocell array is a prefabricated array of higher …

Macrocell – Knowledge and References – Taylor & Francis

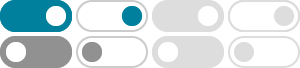

A macrocell is a larger cell made up of grouped cells, typically referred to as a large or medium-sized cell. It comprises AND and OR arrays, a dedicated flip-flop, and control signals for …

macrocell Definition - Intel

A macrocell consists of three functional blocks: the logic array, the product-term select matrix, and the programmable register.

Macrocell array - Academic Dictionaries and Encyclopedias

Essentially, it is a small step up from the otherwise similar gate array, but rather than being a prefabricated array of simple logic gates, the macrocell array is a prefabricated array of higher …

Macrocell array - Semantic Scholar

Programmable logic devices, such as programmable array logic and complex programmable logic devices, typically have a macrocell on every output pin.

L23 — Altera FLEX.ppt - Kent

In this mode, each ESB contains 16 macrocells, and each macrocell contains 2 product terms and a programmable register (parallel expanders also provided) Each ESB can also act as a …

Macrocell array | 1905 Publications | 37383 Citations | Top …

Jun 6, 2001 · An FPGA is an array of logic blocks (cells) placed in an infrastructure of interconnections, which can be programmed at three distinct levels (see Figure 1): (1) the …